### 行政院國家科學委員會專題研究計畫 成果報告

# 超大積體電路之低功率及快速測試架構之探討研究成果報告(精簡版)

計 畫 類 別 : 個別型

計畫編號: NSC 96-2221-E-032-058-

執 行 期 間 : 96年08月01日至97年07月31日

執 行 單 位 : 淡江大學電機工程學系

計畫主持人:饒建奇

計畫參與人員: 碩士班研究生-兼任助理人員: 林奕辰

博士班研究生-兼任助理人員:吳柏翰

處 理 方 式 : 本計畫可公開查詢

中 華 民 國 97年12月16日

## 行政院國家科學委員會補助專題研究計畫成果報告

計畫類別:☑個別型計畫 □整合型計畫

計畫編號: NSC 96-2221-E-032 -058

執行期間: 96年 8月 1日至 97年 7月 31日

計畫主持人: 饒建奇

共同主持人:

計畫參與人員:吳伯翰、林益辰

執行單位:淡江大學電機工程學系

中華民國 97年 7月 4日

#### 超大積體電路之低功率及快速測試架構之探討

"The Study of Low-Power And Rapid Testing Architectures of VLSI"

計畫編號: NSC 96-2221-E-032 -058

執行期間:96年8月1日至97年7月31日

主持人:淡江大學電機工程系教授

#### 一、中文摘要

由於製程與封裝技術快速發展,使得單晶 片系統成為一個趨勢,它是將整個系統所能執 行的功能都由一矽晶片來實現,以至於要從外 部來測試系統有沒有發生錯誤和缺陷變的非 常困難了。所以大部份的設計者在設計晶片的 過程中就會將測試的電路也一併加入,也就是 所謂的可測試設計。內建自我測試是屬於可 試設計的其中一種方法。BIST 的架構裡包含了 輸出回應訊號分析器,測試向量產生器,來當作 測試向量產生器。

由於測試向量是由假性隨機測試向量產生器所產生的,所以需要比較長的時間以及較多的功率消耗,另外,亦無法得到較高的錯誤涵蓋率,而且一些無效的測試向量也會使得測試時間變長,因此為了縮短測試長度,亦即測試時間降低以及測試期間的功率消耗,我們修改了掃描鏈架構,使其可以依照測試需求而縮短長度,另外我們也使用 ATPG 產生的關鍵測試長度以及錯誤涵蓋率。

在本計劃中,我們修改傳統 BIST 測試環境,以及提出搭配的近似演算法。本計畫可以降低測試應用時間以及測試功率的消耗。經過我們提出的演算法後,我們會將測試向量分成數個測試組合排程,然後將此結果對應至我們提出的硬體架構。

#### 英文摘要

Because of modern design and package

technologies were developed fast, make the system-on-a-chip become a trend, it is the function that can carry out the whole system is realized by one chip. Therefore, external testing increasingly difficult and the built-in self-test (BIST) have emerged as a promising solution to the VLSI testing problem. BIST is a design for testability methodology aimed at detecting faulty components in a system by incorporating test logic on-chip. The main components of a BIST scheme are the test pattern generator (TPG), the response compactor, and the output response analyzer (ORA). The test generator applies a sequence of patterns to the circuit under test (CUT), the responses are compacted into a signature by the response compactor, and the signature is compared to a fault-free reference value.

During built-in self-test (BIST), the set of patterns generated by a pseudo-random pattern generator may use longer test time and more power consumption, then it would not provide sufficiently high fault coverage and many patterns were undetected faults (useless patterns). In order to reduce the test time and power consumption in testing, we modify the scan chain architecture and use critical patterns from ATPG to improve test length and achieve high fault coverage.

The proposal intends to modify traditional BIST environment and propose sufficient algorithm to reduce test application time and test power consumption. A given test cubes with unspecified bits that generated by a sequential automatic test pattern generator (ATPG). We can save power consumption and test application time.

#### 二、計畫的緣由與目的

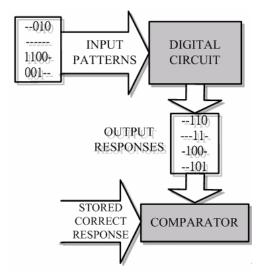

基本的測試原理是將測試向量在電路的輸入端輸入,而測試結果的數值會被與預期的結果做比較,如果與預期的測試結果符合的,那表示晶片是正常的,而預期的結果我們通常稱為 fault-free 值,其為正常無錯誤的情況下,輸入與輸出的對照表。圖1說明了數位電路測試的基本原理。

圖 1: Principle of testing

隨著整合性 IC 發展以及 IP (Intellectual Property Reuse, IP)技術日漸成熟, VLSI 設計逐漸邁入系統單晶片 (System-On-a-Chip, SoC)時代,然而將從前設計的單一功能模組整合進同一個晶片(Chip)中,對於外部測試機台(Automated Test Equipment, ATE)來說,變成複雜的測試環境,也由於不同模組之間特性的差異,使得測試變得非常的困難,而內建式自我測試(Built-In Selt-Test, BIST)剛好是一個良好

的解決方案。

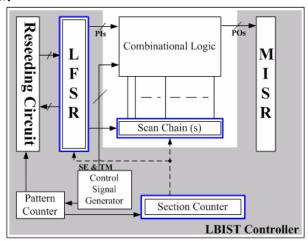

內建式自我測試是一種可測試設計 (Design for Testability, DFT)的電路,設計者在設計晶片的過程中就會將測試的電路也一併加入,其架構大略分為以下三部份:測試向量產生器(Test Pattern Generator, TPG),待測電路(Circuit Under Test, CUT)和信號(向量)結果分析器(Output Response Analyzer, ORA)。圖 2 所表示的是 BIST 的基本架構。

圖 2: Architecture of the BIST

測試向量產生器通常使用線性回溯移位暫存器(Linear Feedback Shift Register, LFSR),負責產生連續的假性隨機測試向量(pseudo-random pattern)給待測電路,測試結果壓縮器負責壓縮測試結果,使它變為一個信號(向量),而所產生的信號(向量)在與fault-free 的值做比較後,經過錯誤診斷分析,我們就能夠知道錯誤所在的位置,並加以處理。

根據國內外學者的研究報告,我們發現在內建式自我測試方法中,由測試向量產生器所產生的假性隨機測試向量可能無法在一定的時間內,提供足夠高的錯誤涵蓋率(Fault Coverage, FC),而且很多測試向量無法偵測錯誤的(useless pattern),這造成使用內建式自我測試方法的時間浪費,因此為了降低測試時間,我們可以將這些無效的測試向量跳過,或是將他們變為有效的測試向量。

另一方面,超大型積體電路的基本原則包含了半導體元件技術,電路設計和電子測試,在達到應用階層之前,電路的測試是必需且迫切的。若將超大型積體電路的領域擴展到系統單晶片,則晶片上包含了:數位電路,記憶體單元和混合信號子系統···等多種單功能晶片模組。因為來自不同的設計者,所以每一種模組或是 IP 的測試方法也不一定相同,對於使用 ATE 由外部輸入測試向量的方式造成很大的困難度,但是針對系統單晶片來說,相對於內建式自我測試變成一個較佳的測試方案。

但是對於內建式自我測試,它本身還是有許多的缺點。由於 BIST 本身的特性,一定會造成晶片額外的電路負擔、測試時間過長…等問題,因此早期的 BIST 研究多著重於降低測試時間的耗損,或是縮小額外的面積增加。但是隨著 VLSI 製程技術的進步,整個電路設計面積釋放,我們不難發現,在最近幾年來 IEEE中,EI、SCI和 SSCI 的幾個指標性期刊或是研討會議中發表的研究報告,幾乎都著重於功率消耗的問題。

功率消耗相關的議題早在 1990 年出就已經有許多學者在研究,但最近幾年來 VLSI 製程 技術 已經 超越 人類 全客戶設計 (Full-Custom Design)的極限,取而代之的是基本元件設計(Cell-Based Design),這種設計方式使用標準元件(Stand Cell)搭配 CAD 軟體技術,大幅拉近製程技術與電路設計之間的差距。而在 Testing 方面,因為早期使用 ATE 由外部輸入測試向量的成本比額外增加測試電路的成本低,因此多採用外部測試,但是隨著製程技術的進步,額外增加測試電路已經不是很大的問題,但相對產生另一個很重要的問題,那就是功率消耗的問題。

根據許多的研究報告指出,當晶片位於測 試模式所花費的功率消耗會比一般使用模式 時高出很多,又因為電路圖的大小倍數增加, 更加重功率消耗,造成功率消耗的問題已經是 迫切需要解決。在功率消耗的問題中,主要是 峰值電壓(Peak Voltage)以及平均功率消耗 (Average Power consuming)。平均功率消耗 會造成能源的浪費,峰值電壓過高,會使晶片 電壓超過本身的負荷值,而造成晶片本身的損 害。

功率消耗簡單來說,就是當電路中發生 01 轉換的時候。在 BIST 的測試方法中,很容易有功率消耗的問題,因此有許多不同的研究都是針對 BIST 所產生的測試向量進行更動,使其 01 轉換的時間點平緩[1],或是降低 01 轉換的次數。本計劃的研究方向將鎖定在降低 01 轉換的次數。

在前面我們提到在BIST中的測試向量產生器,一般由使用LFSR產生假性隨機測試向量,造成在一定的時間內,假性隨機測試向量的錯誤涵蓋率可能無法提高,而無法達到較高的錯誤涵蓋率,所以我們使用自動測試向量產生軟體(Automatic Test Pattern Generation, ATPG)所產生出的測試向量,ATPG軟體所產生的測試向量的錯誤涵蓋率幾乎可以達到100%。

另一方面,為了有效降低功率消耗的問題,我們將 ATPG 軟體產生的測試向量中的不考慮值(don't care)保留,我們希望能夠藉由我們的方法將這些不考慮值填入明確的值,藉以有效的降低功率消耗的問題。

在本次的計畫中,我們將提出一個有效的硬體架構,在增加極少硬體成本的考量下,同時可以解決測試時間以及功率消耗的問題,並依照這個硬體架構,提出一個搭配的近似演算法,去實現這個硬體架構。如果可以有效降低測試時間,並且減少功率消耗,對於VLSI在進入 SOC 時代的測試工程,將有更進一步的幫助。

在電路中加入內建式自我測試的功能,除了可以減少許多外部測試成本,電路測試的彈

性度也相對增加。例如,開機前的自我測試不需要全部由軟體控制,維修工程師尋找錯誤發生位置時也不需要昂貴的補助設備…等,都可以由硬體自行完成,這些都可以加速各方面測試或是維修的進行,也可以有效的分析錯誤的發生位置及原因。另外,對於功率消耗的縮減,更可以擺脫電線的問題,進而轉變成行動式商品,不再侷限於使用的地點。

#### 三、研究方法及成果

在本研究計畫中,我們提出一個新的硬體架構。圖 3 是我們的 BIST 整體測試環境,我們 加 入 了 "Section Counter" 去 控 制 "LFSR" and "Scan Chain(s)",我們亦修改"LFSR" and "Scan Chain(s)"的傳統架構。

圖 3: BIST 環境

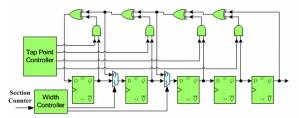

圖 4 是可修改式多重 LFSR 多項式硬體架構,為了讓 LFSR 的架構具有較高的彈性,我們在多重 LFSR 多項式架構 (Multiple Polynomial LFSR, MPLFSR)中增加數個多工器,並由"Width Controller"來變更假性隨機測試向量的長度。舉一個簡單的範例,如果我們將左邊的多工器設定為低電位,右邊的多工器設定為高電位,則為一個 4 個位元的假性隨機測試向量產生器,如果我們將所有的多工器設定為低電位,則為一個 3 位元的假性隨機測試向量產生器。其係數是由"Tap Point Controller"所決定。為了考量多工器設計的

簡易以及方便,我們首先將所有的多工器設定為高電位,並依照 "Width Controller"由左向右,一次將一個多工器設定為高電位。此方法可以讓 "Width Controller"的硬體設計非常簡單,也非常的小。

圖 4: 可修改式多重 LFSR 多項式硬體架構

在經過上面的方法後,我們可以將一個掃描鏈中的位元位置分成兩個不同的群組,但是這些位置可能是不連續的,圖 4.5 中的範例,我們所選擇出來的位元位置並不是連續的,這個問題在參考文獻[1]也有被提及,我們可以將更改過的位元順序直接由目前存在的EDA軟體重新繞線,它可以最佳化繞線路徑的問題,目前的EDA軟體在重新繞線的的方面,已經有很好的成果,所以這個問題我們可以不用太在意。

#### 四、結論與討論

在本研究中,我們針對低平均功率消耗以 及低峰值電壓,提出一個新的硬體架構,這個 架構更可以讓測試時間有效的縮短。實驗結果 中,我們提出的演算法只需要使用很少的測試 排程,而這個表示在第一階段中,測試向量集 合位元位置彼此之間關係越容易合併,我們所 使用的測試排程越少。值得一提的是,如何選 擇位元位置在整個演算法是一個很重要的流 程。本研究群的相關研究結果, 97 年發表會 議論文 2 篇,並於期刊發表一篇論文。目前並 有兩篇期刊論文已經在接受審稿中。

#### 五、參考文獻

[1] N. C. Lai, S. J. Wang, and Y. H. Fu, "Low Power BIST with Smoother and Scan-Chain Reorder", in *Proc. Asian Test Symposium*, pp. 40-45, 2004.