# ISCA 2000 - LETE International symposium on Circuits and Systems, May 28-31, 2000, Geneva-Switzerland

Kuo-Hsing Chen, Huan-Sen Liao, and Lin-Jiunn Tzou Dept. of Electrical Engineering, Tamkang University, Taipei Hsien, Taiwan, R.O.C

TEL: 886-2-26215656 ext 2731 FAX: 886-2-26221565 E-mail: cheng@ee.tku.edu.tw

### Abstract

This paper describes a design of digital phase-locked loop (DPLL), which has low-power consumption and low jitter feature. Novel voltage controlled oscillator (VCO) and phase frequency detector (PFD) are proposed to reduce the total power consumption and phase error of the DPLL. The proposed VCO has low power consumption, and the PFD is a "three-state" structure with dead zone is 5ps. The power consumption of the proposed DPLL is lower than 6.7mW, and the output-frequency range of the oscillator is from 200MHz to 650MHz. The worst-case cycle jitter is lower than 160ps, and long-term jitter is lower than 220ps. We confirm the results based on 0.5um CMOS technology and 3V supply voltage.

#### 1. INTRODUCTION

Phase-locked loop is a basic component used frequently in many analog and digital systems. Phase-locked loop can be used in clock recovery of communication system and frequency synthesizer of wireless communication system[1][6]. Recently, low power consumption has become the main trade -off in the modern VLSI design, owing to fast development of mobile electronic system[7][8]. Thus, the goal of our paper is to design a low power phase-locked loop.

VCO is an important component of the PLL because the VCO dominates the power consumption of PLL. Therefore, we propose a VCO with low power consumption.

The PFD is also an important component reducing the phase error and locked time of the PLL. In general, "three-state" structured PFD has large dead zone; "four-state" structured PFD has large gain, which makes the phase offset of the charge pump when PLL locks. Consequently, the phase error increases. For these reasons, we propose a "three-state" structured PFD with 5ps dead zone to reduce the phase error of the PLL.

### 2. DIGITAL PHASE-LOCKED LOOP OVERVIEW

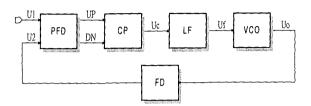

A block diagram of a simple digital phase-locked loop is shown in Fig. 1. At first, the PFD begins to detect the phase error between the reference signal U1 and feedback signal U2. The digital signals of PFD output control the VCO through the charge pump (CP). The loop-filter (LF) can filter the noise and the high-frequency part of output signal of the CP and hold in lock. The frequency divider (FD) is sometimes placed in the feedback loop to make the VCO multiply frequency of the reference signal U1.

Fig 1 . DPLL function block diagram

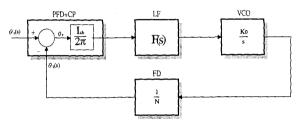

Fig 2. DPLL linear model transfer function

The linear model of this DPLL is shown in Fig. 2[3]. The variables  $\theta$  1 and  $\theta$  2 are the phase of the reference signal U1 and feedback signal U2. The parameter K0 is the gain of VCO, and N is the divisor of the frequency divider. The close-loop transfer function H(s) is

$$H(s) = \frac{\omega_n^2 + 2\zeta\omega_n s}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

$\omega$ n is the nature frequency, and  $\zeta$  is the damping factor.

## 3. LOW POWER VCO DESIGN

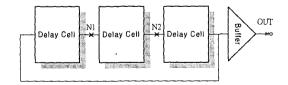

The programmable delay element is an important component in the low-power VCO design. The VCO dissipates much power when output voltage of delay element varies from (VDD-|Vtp|) to (Vtn+VSS). The VCO has large power dissipation due to the large short circuit current flowing from VDD to VSS. As shown in Fig. 3, if the transition time of the node voltage of N1 or N2 from (VDD-|Vtp|) to (Vtn+VSS) is too long, it will cause large short circuit current of the delay element.

Fig 3. The general VCO Block.

0-7803-5482-6/99/\$10.00 ©2000 IEEE

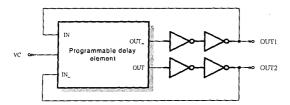

Fig. 4. The proposed low power VCO.

The block diagram of the proposed VCO shown in Fig. 4 has three low-power features: (1)use only one programmable delay element. (2)no short circuit current. (3)the programmable delay element can shorten the output transition time to reduce the short circuit current of the next stage.

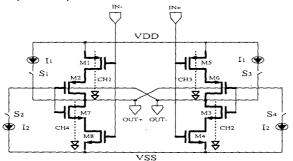

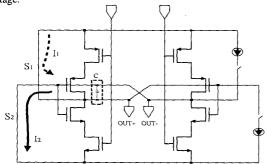

The basic circuit block of the proposed delay element is composed of two C2MOS inverters with four switches and controlled currents shown in Fig. 5. Two C2MOS inverters are connected as a regeneration latch to reduce the time cost of output changing from (VDD-|Vtp|) to (Vtn+VSS). Moreover, owing to the feedback control, the circuit has no short circuit from VDD to VSS. In Fig. 5, the switches S2 · S3 are controlled by the input IN+; the switches S1 · S4 are controlled by the input IN-. If the IN+ rises to high and IN- falls to low, the switch S2 is turned on and current source I2 begins to discharge the OUT-; the switch S1 is turned on and current source I1 begins to charge the OUT+. The voltage of the OUT- decreases slowly. The channel CH1 hasn't been turned on until the OUT- decreases lower than (VDD-Vtpl). Then voltage of OUT+ is charged to VDD quickly. In the same way, the voltage of the OUT+ increases slowly. The channel CH2 hasn't been turned on until OUT- increases higher than (Vtn+VSS). And then the voltage of OUT- is discharged to VSS quickly. The result is shown in Fig. 6. During the transient time, no short circuit current flows from VDD to VSS because only channels CH1 and CH2 are turned on.

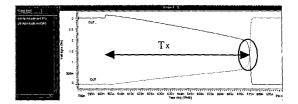

In the reverse case, the IN- rises to high and IN+ falls to low. The channel CH3 is turned on and then OUT- is charged to VDD fast; the channel CH4 is turned on and then OUT+ is discharged to VSS quickly. Since only channels CH3 and CH4 are turned on, no current flows from VDD to VSS, either. In Fig. 6, the output of the programmable delay element has very short transition time; therefore it can reduce the short circuit current of the next stage. As a result, the proposed programmable delay element can reduce the power dissipation of the VCO.

Fig 5. The circuit of the proposed programmable delay element.

**Fig 6.** The output waveform of the proposed programmable delay element.

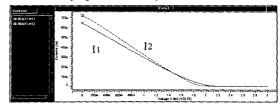

Fig 7. The controlled currents I1 · I2.

The control current I2 is used to discharge the output nodes of the proposed programmable delay element from VDD to (VDD-|Vtp|), and this time cost is the main delay time Tx. The capacitive load of the output node also controls the delay range of the delay element.

In order to get a better linearity between input voltage and output frequency in VCO, the controlled currents II \cdot I2 must have good linearity, as shown in Fig. 7. The controlled voltage range of the proposed element is from 0V to 1.8V.

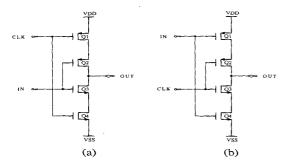

In general, the C<sup>2</sup>MOS inverter has two circuit structures, as shown in Fig. 8. The circuit shown in Fig. 8(a) has the charge sharing problem because the signal IN changes faster than the signal CLK. This makes Q2 or Q3 turned on too quickly. It makes the output OUT has charge sharing with parasitic junction capacitance. Charge sharing makes incorrect charge and discharge and causes the deviation of delay time. In order to reach the high frequency stability and small phase error in the VCO, the circuit shown in Fig. 8(b) is used.

The problem clock feedthrough is a charge injection error on the output nodes, which brings unwanted charge into output nodes. In the Fig. 9, when the current source 12 discharge the node OUT-, the voltage of the output OUT+ reduces a  $\Delta V$  from zero because the coupling effect of the parasitic capacitance. The clock feedthrough problem causes a variation of delay time, making an unbalance of the duty cycle of the delay element. And then the phase error of VCO will increase. In order to cancel the clock feedthrough problem, we add two current sources I1 to compensate the coupling effect.

The integrated circuit of proposed programmable delay element is shown in Fig. 10.

Fig 8. The C<sup>2</sup>MOS inverters.

The simulation results of the proposed VCO are shown in Table 1. The highest frequency of the proposed VCO is 650MHz. As the output frequency is lower than the 200MHz, the jitter will increase. Thus the turning range of the proposed VCO is from 200MHz to 650MHz for low jitter application. The total power of the VCO is lower than 4.86mW. This shows the short circuit current has been reduced in the proposed delay element. The design is based upon 0.5  $\mu$  m CMOS technology with 3V supply voltage.  $$^{\rm IN-}$$

Fig. 9 The clock feedthrough problem.

Fig. 10 The schematic of proposed programmable delay element.

| · · · · · · · · · · · · · · · · · · · | Frequency | Power |

|---------------------------------------|-----------|-------|

| Controlled Voltage (V)                | (MHz)     | (mW)  |

| 0.1                                   | 662       | 4.86  |

| 0.2                                   | 650       | 4.77  |

| 0.4                                   | 627       | 4.55  |

| 0.6                                   | 590       | 4.29  |

| 0.8                                   | 550       | 3.98  |

| 1.0                                   | 500       | 3.60  |

| 1.2 | 437  | 3.20 |

|-----|------|------|

| 1.4 | 367  | 2.76 |

| 1.6 | 278  | 2.20 |

| 1.8 | 174  | 1.50 |

| 2.0 | 77 . | 1.30 |

Table 1. The simulation results of the proposed VCO.

# 4. "THREE-STATE" PFD with 5ps DEAD ZONE DESIGN

$$I_{d} = I_{ch} \times \frac{\Delta \theta}{2 \pi} = \frac{I_{ch}}{2 \pi} \times \Delta \theta = K_{d} \times \Delta \theta$$

The first component of the DPLL is PFD, which controls the locked time and jitter of the DPLL. The output of the PFD depends on both the phase and frequency of its inputs. It compares the leading edges of the reference signal U1 and feedback signal U2. If the phase error is  $\Delta \theta$ , the output average current of charge pump can be written as

where Kd is the gain of PFD, Ich is the current source of charge pump.

Dead zone is an important parameter of the PFD. And not all PLL using no dead-zone PFD can have the better jitter because the VCO also has the jitter. And the PFD can not detect this random jitter. A good way is to use the PFD with few dead zone. In this way, we can reduce the gain of the PFD of when PLL in locked, and reduce the charge or discharge time of the charge pump.

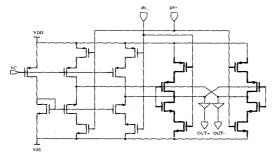

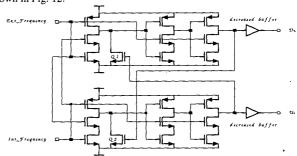

We propose a "three-state" PFD with dead zone is 5ps shown in Fig. 11[2][4][5]. When frequency of the U1 and U2 are equal, the outputs of PFD have glitches due to the internal race problem of the dynamic logic. We reduce the gain of PFD and place a decreased buffer to reduce the glitches. The output waveform is shown in Fig. 12.

Fig 11. The schematic of proposed phase frequency detector

# 5. CHIP LAYOUT AND SIMULATION RESULTS

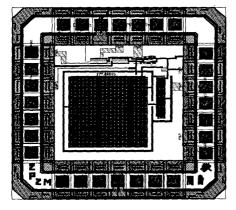

The chip Layout of the proposed low-power PLL is shown in Fig. 12, the total area is  $0.837 \mathrm{mm}^2$ . The simulation results of the proposed PLL are shown in Table 2 and Table 3. The total power of the proposed PLL is lower than 6.7 mW, and cycle jitter is smaller than 160 ps. The design is based upon  $0.5~\mu$  m CMOS technology with 3V supply voltage.

| VCO OUTPUT<br>FREQUENCY | POWER<br>CONSUMPTION | LOCKED<br>TIME | CYCLE | LONG-<br>TERM<br>JITTER |

|-------------------------|----------------------|----------------|-------|-------------------------|

| 650MHz                  | 6.7 m W              | 2.7us          | 23ps  | 80ps                    |

| 500MHz                  | 5.8 m W              | 18.8us         | 10ps  | 45ps                    |

| 400 M H z               | 5.2mW                | 18.8us         | 30ps  | 80ps                    |

| 300MHz                  | 4.6m W               | 18.6us         | 100ps | 160ps                   |

| 200MHz                  | 4.1 m W              | 17.1us         | 160ps | 22ps                    |

| without noise           |                      |                |       |                         |

Table 2. The simulation results of the proposed PLL.

| TECHNOLOGY         | UMC 0.5UM 2P2M CMOS            |

|--------------------|--------------------------------|

| Supply Voltage     | 3V                             |

| Chip Area          | $0.924 \times 0.9 \text{mm}^2$ |

| Input Locked Range | 50MHz∼162.5MHz                 |

| Power Consumption  | 3.6mW~6.7mW                    |

| Locked Time        | 2.7us~18.8us                   |

| Long-Term Jitter   | 45ps∼220ps                     |

| Cycle Jitter       | 10ps∼160ps                     |

| Bandwidth          | 509.6kHz                       |

| Damping Factor     | 0.16                           |

Table 3. The specification of the proposed PLL.

Fig 11. The output waveform of PFD

Fig 12. The chip of the proposed PLL

#### 6. CONCLUSION

In this paper, a low power DPLL has been proposed and analyzed. And a low-power programmable delay element is proposed in this design of the PLL. This work proposes novel voltage control oscillator and phase frequency detector to reduce the total power consumption and phase error of the DPLL. The programmable delay element of the proposed VCO has three features: (1) use only one programmable delay element. (2) no short circuit current. (3) the programmable delay element can shorten the output transition time to reduce the short circuit current of the next stage. The power consumption of the PLL is lower than 6.7mW. The worst-case cycle jitter is smaller than 160ps, and long-term jitter is samller than 220ps. The frequency range of VCO is operated from 200MHz to 650MHz. The chip of proposed DPLL is implemented with 0.5um CMOS process technology. The layout area of the chip is 0.837mm<sup>2</sup>.

#### 7. REFERENCE

- [1] C. Hyeon et al., "Design of Low Jitter PLL for Clock Generator with Supply Noise Insensitive VCO," *IEEE international Symposium on Circuits and Systems* 1998 vol. 1, pp. 233-236.

- [2] H. Kondoh et al., "A 1.5 V 250 MHz to 3.0 V 622 MHz Operation CMOS Phase-Locked Loop with Precharge Type Phase-Frequency Detector," *IEICE Trans. Electron*, vol. E78-C, no. 4, pp. 381-388, April, 1995.

- [3] F. Gardner et al., "Charge-Pump Phase-Lock Loops, "IEEE Transaction on Communications, vol. com-28, no. 11, pp. 1849-1858, Nov 1980.

- [4] S. Kim et al., "A 960-Mb/s/pin Interface for Skew-Tolerant Bus Using Low Jitter PLL," *IEEE Journal of Solid-State Circuits*. vol. 32, no. 5, pp. 691-699, MAY 1997.

- [5] H. Johansson et al., "A Simple Precharged CMOS Phase Frequency Detector", *IEEE Journal of Solid-State Circuits*. vol. 33, no. 2, pp. 295-299, Feb. 1998.

- [6] I. Novof et al., "Fully Integrated CMOS Phase-Locked Loop with 15 to 240 MHz Locking Range and ±50 ps Jitter," *IEEE Journal of Solid-State Circuits*, vol. 30, no. 11, pp. 1259-1266, Nov. 1995.

- [7] V. Kaenel et al., "A 320 MHz, 1.5 mW @ 1.35 V CMOS PLL for Microprocessoer Clock Generation," *IEEE Journal of Solid-State Circuits*, vol. 31, no. 11, pp. 1715-1722, Nov. 1996.

- [8] J. Maneatic et al., "Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques" *IEEE Journal* of Solid-State Circuits, vol. 31, no. 11, pp. 1723-1732, Nov. 1996.